Discussion

This discussion assumes you are familiar with the general principles behind pull-up resistors.

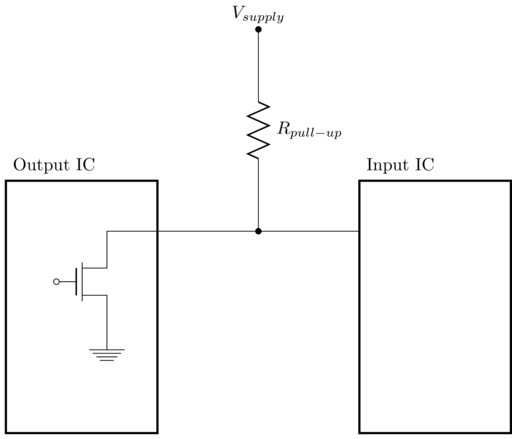

The circuit being analyzed has two sides. The output side outputs an open-drain logic state, and the input side receives a push-pull logic state. The pull-up resistor must meet two criteria:

- When output is logic-high, and therefore in high impedance state, signal voltage has to exceed minimum logic-high voltage of input

- When output is logic-low, and therefore tied to ground, signal voltage must not exceed maximum logic-low voltage of input or output

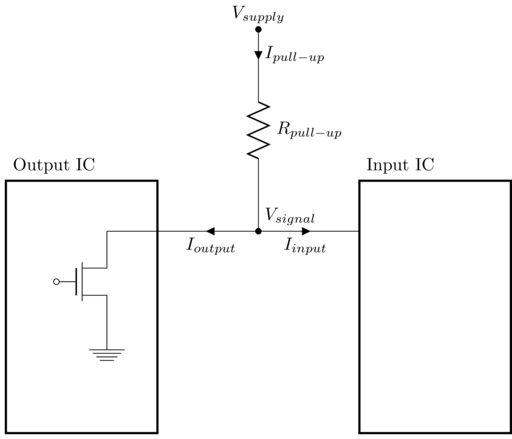

Logic-high

In the first case (logic-high), the supply is sourcing current, output is leaking some current to ground, and the rest of the current is going to input:

The lowest value of

Component parameters that determine viable values of the pull-up resistor are:

- Minimum supply voltage

- Maximum current on output in logic-high state, also known as open-drain leakage current

- Maximum current on input

- Minimum input logic-high voltage

Which leads to:

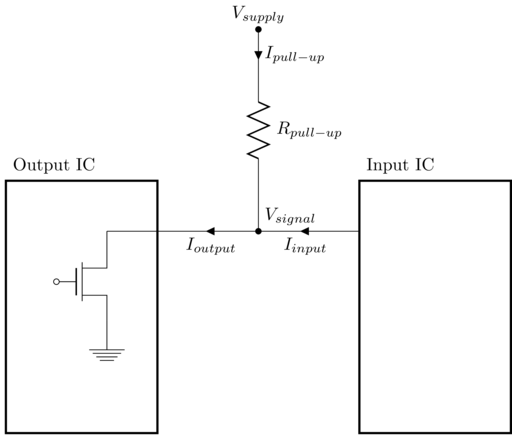

Logic-low

In the second case (logic low), the supply is sourcing current, output is sinking this current to ground, and input is leaking some current, which output is also sinking to ground:

Signal voltage

The highest value of

Signal voltage minimum is zero; other component parameters that determine viable values of the pull-up resistor are:

- Maximum supply voltage

- Maximum current on input, also known as bias current

- Maximum output logic-low current

Therefore:

Additionally,

However, since the relationship between output sink current and signal voltage is generally unknown, when maximum logic-low voltage for input is below the maximum logic-low voltage for output, there is no definitive way to calculate the range of viable pull-up resistors. The only option is to err on the side of larger pull-up resistor values.

Acknowledgements

This calculator and the discussion are based on information from TI Application Report SLVA485 by Ben Hopf.